ヘテロ接合型結晶セレン光電変換膜を積層したイメージセンサーの開発

将来の超高精細映像システムの実現を目指して,結晶セレン(c-Se:crystalline Selenium)を光電変換膜に用いたイメージセンサーの研究開発を進めている。光電変換材料として,これまで一般的に用いられてきたシリコン(Si)に替えて,可視光領域において高い光吸収特性を有するc-Seを用いることにより,光電変換膜内でのアバランシェ(なだれ)増倍を利用した高感度イメージセンサーが実現できる。今回,ガラス基板上に作製した試作膜において,c-Seで初めてアバランシェ増倍を確認し,100%を超える量子効率が得られた。また,CMOS(Complementary Metal Oxide Semiconductor)回路上に一様なc-Se膜を作製することにより,高画質な映像の撮影に成功した。

1.はじめに

当所では,多画素化や高フレームレート化が進むテレビカメラの感度不足の問題を抜本的に解決するために,信号電荷のアバランシェ(なだれ)増倍*1 が可能な光電変換膜をCMOS回路上に積層した新たな高感度イメージセンサーの研究開発を進めている。

アバランシェ増倍を利用した代表的な高感度イメージセンサーとしては,アモルファス(非晶質)セレン(a-Se)を光電変換膜に用いた超高感度HARP(High-gain Avalanche Rushing amorphous Photoconductor)撮像管があり1)2),放送用途以外にも医療や理学など幅広い分野で利用されてきた。しかし,a-Seでアバランシェ増倍に必要な電界を得るためには,CMOS回路の耐電圧を超える高い電圧(実用化されているHARP撮像管では約1,500V)を印加する必要があることから,それに替わる新たな光電変換材料への期待が高まっていた。

低電圧での電荷増倍を実現するために光電変換材料に求められる条件としては,可視光に対して高い光吸収特性を有し,薄膜化が可能であることが挙げられる。結晶セレン(c-Se)は,可視光用イメージセンサーの光電変換材料として一般的に用いられているシリコン(Si)と比べても光吸収係数*2 が一桁以上高く(1図),膜厚を500nm以下に薄くしても可視光を十分に吸収できることから,有望な材料と考えられる。

今回,c-Seを用いてガラス基板上に試作した光電変換膜において,初めてアバランシェ増倍により100%を超える量子効率*3 が得られることを確認するとともに,CMOS回路上に一様なc-Seを形成することで,高画質な映像の撮影に成功した。

本稿では,試作膜の作製プロセスと特性について述べた後,撮像実験の結果や結晶粒径と画質の関係について報告する。

2.光電変換膜の作製

本章では,c-Seを用いた試作膜の作製プロセスについて述べる。

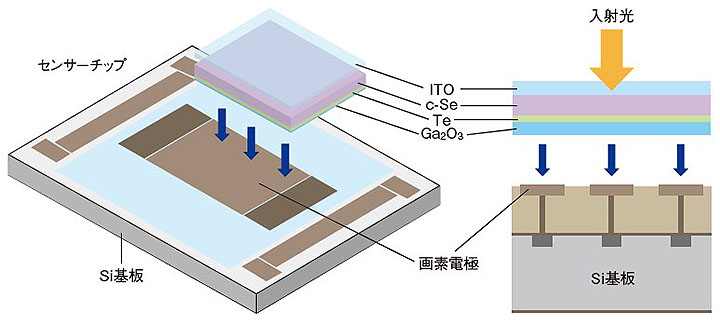

ガラス基板上に作製した光電変換膜の断面図を2図(a)に,また,CMOS回路上に作製した光電変換膜の概略図と断面図を2図(b)に示す。下部電極として,2図(a)では透明導電膜であるITO(Indium Tin Oxide:酸化インジウムスズ)を,2図(b)では画素ごとにパターン形成された金属電極を用いた。

作製プロセス(2図(a)と(b)で共通)は次の通りである。まず,下部電極上にRFスパッター法*4 により酸化ガリウム(Ga2O3)を直接成膜した。その上にSe膜の剥離を防止するためのテルル(Te)をごく薄く成膜した後,真空蒸着法*5 によりa-Seを成膜した3)。次に,作製したa-Seに対して,大気中で200℃の加熱による結晶化を行い,c-Seを作製した。a-Seとc-Seの外観の比較を3図に示す。最後に,DCスパッター法*6 により上部電極として透明導電膜ITOを成膜し,光電変換膜を作製した。

3.試作した光電変換膜の特性

ガラス基板上に試作した光電変換膜 (2図(a)) について,逆バイアス*7(上部電極が陰極)印加時の暗電流特性,光電変換特性を調べた。

3.1 暗電流特性

(1) Te層厚の影響

上述したように,Se結晶化時の膜剥がれ防止のために,極めて薄いTe層をGa2O3とc-Seの間に挿入している。Teはc-Se内でアクセプター*8 として振る舞うことが知られており,暗電流の要因となり得る。この点について検討するために,ガラス基板上にTeを0.1nm成膜し,その上にa-Seを100nm成膜して,加熱によりc-Seを作製した後,c-Se内のTeの分布を二次イオン質量分析法(SIMS:Secondary Ion Mass Spectrometry)*9 により測定した。その結果を4図に示す。この図より,加熱によるSeの結晶化の際に,界面に挿入されたTeがc-Se内に20nm程度拡散することが分かる。

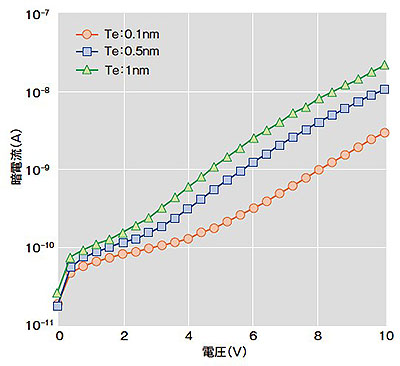

また,5図に, Te層厚の異なるITO/c-Seショットキーダイオード*10 の暗電流の測定結果を示す。この結果から,Te層厚の増加とともに暗電流が増加しており,Te層厚が暗電流特性に大きく影響することが分かる。

以上の検討結果から,暗電流を減らすためには,成膜時の制御が可能な範囲で,Te層厚はできる限り薄くする方が良いと考えられる。今回の試作では,この点を考慮して,Te層厚を0.1nmとして光電変換膜を作製した。

(2) Ga2O3の適用による暗電流の抑制

6図に,ITO/c-SeショットキーダイオードとGa2O3/c-Seヘテロ接合ダイオード*11(2図の光電変換膜と同じ構造のダイオード)の暗電流特性を比較して示す。p型半導体であるc-Seに対してn型半導体としてGa2O3を適用し,pn接合を形成することで,暗電流を大幅に抑制できることが分かる4)。この結果は,7図に示すエネルギーバンド図*12 から直感的に理解できる。バンドギャップ*13 が4.7eV*14 と大きいGa2O3を適用することで,価電子帯*15 におけるITO電極とGa2O3との間の大きなエネルギー差(ΔEv)が,電極からの注入電荷(この場合は正孔)に対する障壁として効果的に働き,高電界印加時の暗電流を大幅に抑制していると考えられる。

Ga2O3/c-Seヘテロ接合ダイオードの暗電流特性の比較

Ga2O3/c-Seヘテロ接合ダイオードのエネルギーバンド図

3.2 光電変換特性

8図に,Ga2O3/c-Seヘテロ接合ダイオードにおける光照射時の電流-電圧特性を示す。Ga2O3中のキャリア濃度が光電変換特性に与える影響を調査するために,スズ(Sn)の添加濃度が異なる3種類のGa2O3(Sn濃度:0%,5mol%*16,5.6mol%)を作製した5)。測定は,入射光の波長が450nm,入射光の強度が2.5µW/cm2の条件下で行った。8図より,いずれの試作デバイスにおいても,信号電流が一度飽和した後,印加電圧20V前後で再び増加する現象が見られており,膜内でのアバランシェ増倍を確認することができた。また,Ga2O3中のSn添加濃度が増加するに伴い,信号電流の飽和や電荷増倍に要する印加電圧を低減できることが分かる6)。この結果は,空乏層の観点から説明できる。すなわち,Ga2O3(n型)とc-Se(p型)の界面に形成される感度領域*17 である空乏層は,c-Seよりキャリア濃度の低いGa2O3側に優先的に広がるため,c-Se側に空乏層を広げるためには電圧の印加が必要となる。しかし,Sn添加によりGa2O3のキャリア濃度を増加させることで,c-Seとの間のキャリア濃度差が小さくなり,低電圧でc-Se側に空乏層が広がるため,効率的な光電変換動作が可能となる。

9図に印加電圧が異なる場合のGa2O3(Sn濃度:5mol%)/c-Seヘテロ接合ダイオードの分光感度特性(光の波長ごとの量子効率)を示す。印加電圧2Vのときは空乏層がGa2O3側に広がり,可視光に対する感度が極めて低いのに対して,印加電圧を信号電流が飽和する15Vまで大きくした場合,c-Se側に空乏層が十分に広がることで,可視光領域において高い量子効率が得られた。さらに電荷増倍領域である23Vまで印加電圧を大きくすることで,c-Seで初めて100%を超える量子効率を確認した。

ダイオードの光照射時の電流.電圧特性

ヘテロ接合ダイオードの分光感度特性

4.撮像特性

本章では,c-Se膜をCMOS回路上に作製し,その撮像特性を評価した結果について述べる。

10図(a)~(d)に,膜厚が2µm~200nmのc-Se膜の表面を,走査型電子顕微鏡(SEM:Scanning Electron Microscope)*18 により観察した二次電子線像*19 を示す。c-Seの結晶粒径に注目すると,膜厚が厚くなるほど粒径が大きくなることが分かる。これは,加熱によるSeの結晶化時に,微量に挿入されたTeを結晶核として,結晶粒が膜厚方向に成長するため,膜厚が厚くなるほど結晶が大きく成長することを示している。

次に,膜厚が2μmと500nmのc-SeをCMOS回路上に作製し,撮像評価を行った(11図(a),(b))。今回,Teの挿入により,一様なc-Se膜の作製が可能になったことで,c-Seを用いた光電変換膜において初めて高画質な映像の撮影に成功した。11図の撮像画像を比較すると,膜厚が薄い,つまりc-Seの粒径の小さい方が,明らかに固定パターンノイズの少ない高画質な撮像画像が得られている。これは,今回用いたCMOS回路の画素サイズである3µmよりもc-Seの粒径が十分小さくなることで,粒子ごとの感度ムラが画素内で平均化されたためと考えられる。

5.まとめ

将来の超高精細映像システムの実現を目指して,ヘテロ接合型結晶セレン光電変換膜を積層したイメージセンサーを開発した。

今回,ガラス基板上に作製した試作光電変換膜において,ワイドギャップ半導体であるGa2O3をn型半導体として用い,c-Seとの間でpn接合を形成し,外部電極からの注入電荷を阻止することで,暗電流の大幅な低減に成功した。暗電流の抑制により,同時に光電変換膜への安定した電界の印加が可能となった結果,c-Seにおいて約20Vの印加電圧でアバランシェ電荷増倍を確認することができ,初めて100%を超える量子効率が得られることを実証した。

また,Teを結晶核としたSeの結晶化により,一様な結晶膜の作製が可能となることで,c-Seを光電変換膜としてCMOS回路上に積層することが可能となった。さらに,c-Seの結晶粒径を膜厚により制御し,画素サイズよりも十分小さくすることで,固定パターンノイズを大幅に抑制した高画質な映像の撮影に成功した。

今後は,ガラス基板上における試作デバイスで実証したアバランシェ電荷増倍による高感度化技術をCMOS回路上においても実現し,超高感度CMOSイメージセンサーの開発に取り組んでいく。

謝辞 c-Se作製に関してご協力いただいた東京理科大学総合研究機構 中田時夫教授,CMOS回路の提供,およびデバイス構造に関して議論いただいたパナソニック(株) オートモーティブ & インダストリアルシステムズ社 沖野徹氏,廣瀬裕氏,加藤剛久氏,パナソニックセミコンダクターソリューションズ(株) 松長誠之氏,兵庫県立大学 寺西信一氏に感謝いたします。

本稿は,Applied Physics Letters誌,およびIEDM Technical Digestに掲載された以下の論文を元に加筆・修正したものである。

S. Imura, K. Kikuchi, K. Miyakawa, H. Ohtake and M. Kubota:“Low-Voltage-Operation Avalanche Photodiode Based on n-Gallium Oxide/p-Crystalline Selenium Heterojunction,” Appl. Phys. Lett.,104,24,pp.242101-1.242101-4(2014)