5.1 撮像技術

RGB積層型撮像デバイスの画質改善の研究

小型で高精細なカラーカメラの実現を目指して、有機光電変換膜(有機膜)を用いた単板カラー撮像デバイスの研究を進めている。有機膜は特定の色の光だけを吸収して電気信号に変換し、その他の色の光を透過するため、複数の有機膜を積層することにより、デバイスの深さ方向で色分離が可能な撮像デバイスを実現できる。2020年度は、CMOSイメージセンサー(CIS)上に2種類の有機膜を積層した3層カラー撮像デバイスの試作と、信号増幅型画素回路の開発に取り組んだ。

3層カラー撮像デバイスの試作では、まず、赤色光を電気信号に変換するCIS上に、有機膜からの電気信号を読み出すための透明な薄膜トランジスター(TFT)アレーと緑色光にのみ感度を持つ有機膜(緑色用有機膜)を形成し、赤/緑の2層構造のデバイスを形成した。このデバイスに、2019年度に開発した、透明なTFTアレーと青色用有機膜をガラス基板上に形成した青色用デバイスを重ね合わせることで、3層カラー撮像デバイスを構成した(図5-1)。試作した撮像デバイスの画素数はQVGA(320×240)、画素ピッチは20µmであり、フレーム周波数60Hzのカラー映像出力が得られた(図5-2)(1)。

一方、これまでのTFTアレー内の画素回路は1つのトランジスターによる電流読み出し方式であり、外部ノイズの影響を受けやすいという課題があった。そこで、画素内に増幅回路を備え、電圧で信号を読み出す信号増幅型画素回路の開発に着手した。この回路を実現するためには、画素内に3つのTFTを集積する必要がある。そこで、まず、増幅回路を設計し、回路シミュレーションによりQVGA画素数でフレーム周波数60Hzでの駆動が可能なことを確認した。つぎに、TFTのチャネル長(2µm)の微細化に取り組んだ。微細化に必要なTFT形成プロセスを開発し、ステッパー露光を導入することでチャネル長を1µmまで微細化した。このTFTを用いて信号増幅型画素回路を試作し(図5-3)、QVGA画素数でフレーム周波数を60Hz駆動とした場合の1フレーム読み出し期間である約35µs以内で読み出し動作が完了することを実証した(2)。

この研究の青色用有機膜の開発は、日本化薬(株)と共同で実施した。

電荷増倍型撮像デバイスの高SN化の研究

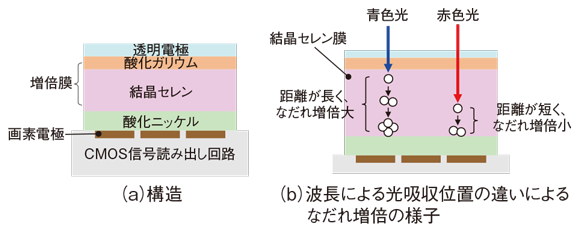

8Kスーパーハイビジョンカメラの高感度化を目指して、電荷増倍機能を有する結晶セレン光電変換膜(増倍膜)を適用したCMOS固体撮像デバイスの開発を進めている。2019年度までに、電子がCMOS信号読み出し回路の画素電極から増倍膜へ注入されて画面上の白傷の原因となることを阻止するために、電子ブロッキング層として酸化ニッケル膜を用い、増倍時の画質を大幅に改善できる技術を開発した。2020年度は、この技術による電荷増倍動作の詳細な検証と、増倍膜のさらなる暗電流の低減、増倍率の増大、そしてCMOS信号読み出し回路の低ノイズ化を進めた。

増倍膜の動作検証について、2019年度に試作した撮像デバイスを用いて、波長による電荷増倍率の違いを調べた。その結果、青色光を入射したときの増倍率(約1.4倍)と比較して、赤色光では増倍率が小さくなること(約1.2倍)がわかった。これは、青色光は結晶セレン膜の光吸収率が高く、膜の浅い位置で電荷が生成される一方、赤色光は光吸収率が低く、主に膜の深い位置で電荷が生成されるため、増倍膜内部での電荷の走行距離が異なり増倍率に差が生じたと考えられる。この特性は、電荷増倍が増倍膜内での電荷のなだれ増倍現象であることを示唆している(図5-4)(3)。また、膜剥がれ防止のためにわずかに添加していたテルル原子が、結晶セレン膜内で拡散してセレン-セレン間の結合を切り離して欠陥となり、暗電流の発生源になることを明らかにした。この対策として、新たに塩素原子を添加することにより暗電流の発生を抑制できる見込みを得た(4)。

増倍率のさらなる向上に向けて、単結晶サファイア基板上に形成した増倍膜を回路上に接合する技術の開発に引き続き取り組んだ。サファイア基板上では、結晶セレンと酸化ガリウムを組み合わせて使用するが、このような接合構造ではCMOS回路の耐熱温度を気にする必要がないため、800℃という高温で結晶化できる。そのため、増倍膜全体の結晶配向性が向上し、より高い増倍率を実現できる。2020年度は、サファイア基板上で結晶化した酸化ガリウムを含む各層を製膜した後、ガラス基板上に非晶質セレン膜を介して加圧接合し、さらにセレンを結晶化するための加熱(160℃)を施した素子を試作した(図5-5)。評価の結果、膜印加電圧18Vにおいて約10倍の増倍率が得られた(5)。さらに、本接合構造での画像取得に向けて、前述の酸化ニッケル膜および、塩素添加も適用し、信号読み出し回路上への接合を進めた。

CMOS信号読み出し回路については、2019年度に開発した、増倍膜と画素電極の浮遊容量を電気的に分離して電荷-電圧変換利得を高めた回路の残像特性などを改善するとともに(6)、浮遊拡散層(膜からの電荷を電圧に変化する容量)のリセット動作時に発生するノイズを抑制する回路を検討した。さらに、これらの結果を反映した増倍膜用の信号読み出し回路の設計を進めた。

これらの研究の一部は、東京理科大学と共同で実施した。

コンピュテーショナルフォトグラフィー基盤技術の研究

物体の高精度な3次元情報取得を目指して、コンピュテーショナルフォトグラフィーの研究を進めている。コンピュテーショナルフォトグラフィーは、レンズで結像した物体像を撮影する従来の撮像手法とは異なり、干渉や光透過マスクにより変調された光の情報を基に、計算で物体像を再構成する手法である。2020年度は、インコヒーレントデジタルホログラフィー(IDH)による物体の3次元情報取得と、低解像度の情報から高解像度の画像を再構成する符号化撮像による手法の原理検証を進めた。

通常のホログラフィーは干渉性の高いレーザー光を照明光として使うが、IDHでは自然光やLED光など、干渉性の低い照明を使用して干渉縞を形成する手法で、撮影した干渉縞からホログラムを取得し、物体像を再構成する。ホログラムには光の振幅と位相の情報が含まれているため、逆伝搬計算により物体の形状や明暗に加えて、3次元情報を取得できる。今回、LED光で照明した物体からの光を2つに分け、両者の相対的な位相を変えることで複数枚の干渉縞を撮影してホログラムを得る光学系を構築し、3次元物体の撮像実験を行った(図5-6)。その結果、取得したホログラムから、計算により任意の位置に焦点を合わせた物体像を再構成することができた(図5-7)。加えて、干渉縞の撮影時における撮像素子のランダムノイズが再構成画像に与える影響を調べ、撮像時のノイズが再構成画像には粒状ノイズとして現れること、また、粒状ノイズは物体までの距離が遠くなるほど拡散されて少なくなることを明らかにした(7)。

符号化撮像については、物体からの光の一部を反射するマスクを光学系中に配置し、そのマスクのパターンやマスクと撮像素子の相対位置を変化させて物体を撮影する実験を行った。撮影した複数枚の低解像度画像から、計算で高解像度画像を再構成した。得られた画像の解像度は、撮影に用いられたすべての低解像度画像の画素数を合計したものよりも高いものであった。