研究内容紹介

6.1 撮像技術

■3次元構造撮像デバイスの研究

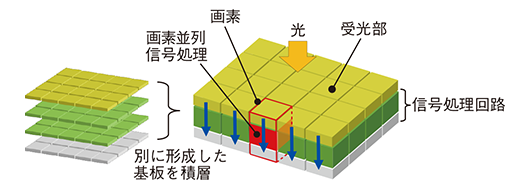

超多画素と高フレームレートを両立する次世代のイメージセンサーの実現を目指して、3次元構造撮像デバイスの研究を進めている。本デバイスは、異なる基板に形成した受光部や信号処理回路を接合して製作することにより、受光部直下に画素ごとに信号処理回路を集積した構造を備えている(図6-1)。これにより、全画素並列に信号処理を行うことで、多画素でも高いフレームレートを維持することができるため、将来の立体映像の取得などへの応用が期待される。

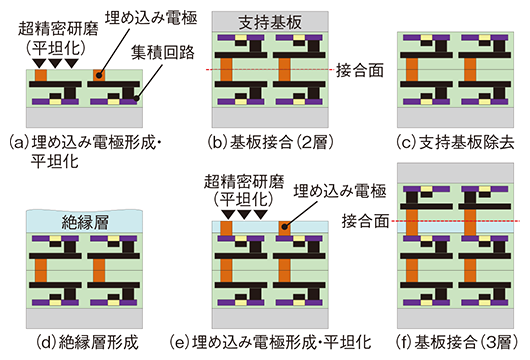

2018年度は、デバイスの高集積化に向けて、3層以上の構造(1)を実現する多層化プロセスを開発した(図6-2)。2層構造を形成する技術(図6-2(a)~(c))に加えて、新たに集積回路の裏面に絶縁層と埋め込み電極を形成する技術と、裏面側の平坦化技術(図6-2(d)~(e))の開発により、3層構造デバイスの試作に成功した。本プロセスの繰り返しにより、さらなる多層化の実現性が高まり、従来平面状に形成してきた信号処理回路を3次元構造化することで、画素サイズの縮小と信号処理回路の高集積化の両立に向けた見通しを得た。

この研究は、東京大学と共同で実施した。

図6-1 3次元構造撮像デバイス

図6-2 多層化プロセス

■RGB積層型撮像デバイスの研究

小型・軽量で機動性に優れた単板カラーカメラの実現に向けて、RGB積層型撮像デバイスの研究を進めている。本デバイスは、赤(R)、緑(G)、青(B)のそれぞれに感度を持つ有機光電変換膜(有機膜)と、各有機膜で発生した信号を読み出す薄膜トランジスター(TFT)アレイとを交互に積層したものである。2018年度は、デバイスの高精細化に向けて、TFTアレイの微細化に取り組んだ。

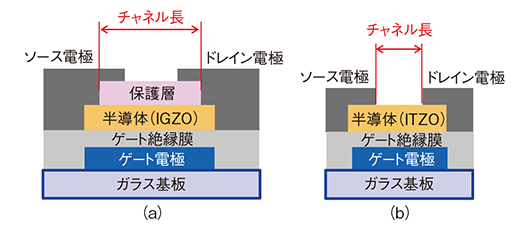

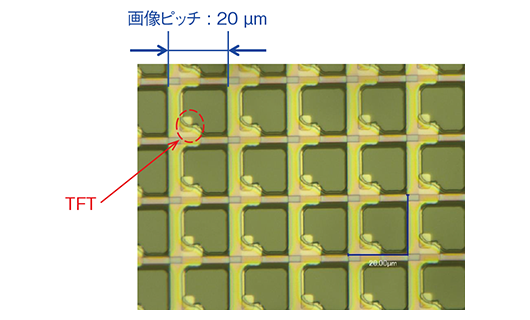

従来のTFTアレイは、半導体にインジウム・ガリウム・亜鉛複合酸化物(IGZO)を用い、ソース・ドレイン(S/D)電極の加工の際に半導体を保護するための層を設けたエッチストップ構造(図6-3(a))としていた。しかし、TFTアレイのさらなる微細化を進めるためには、構造を簡素化する必要があった。そこで、保護層が不要で、エッチストップ構造よりもTFTのチャネル長を短くできるバックチャネルエッチ構造(図6-3(b))を採用した。本構造では、半導体上で直接S/D電極を加工する必要があるため、電極形成プロセスに耐性のある半導体材料としてインジウム・スズ・亜鉛複合酸化物(ITZO)を選択した。これらの製作手法や材料を導入することにより、チャネル長を従来の6μmから2μmに短縮したTFTを試作し、撮像デバイス用の信号読み出しTFTとして108以上の十分なON-OFF比が得られることを確認した。このTFTを用いることで、信号読み出し用TFTアレイの画素ピッチを従来の50μmから20μmに微細化することができ(図6-4)(2)、RGB積層型撮像デバイスの高精細化に見通しを得た。

図6-3 (a)エッチストップ構造TFTと(b)バックチャネルエッチ構造TFT

図6-4 試作したTFTアレイの顕微鏡写真

■固体撮像デバイスの超高感度化に向けたプレーナー型光電変換膜構造の研究

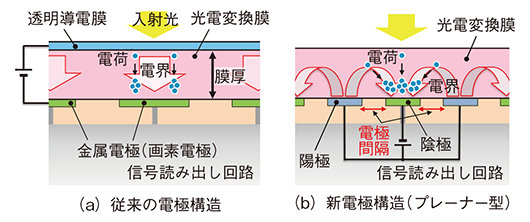

2章2節で、8Kカメラの高感度化を目指した増倍膜積層型8K固体撮像デバイスの研究について述べた。このデバイスでは、アバランシェ増倍現象による電荷増倍に必要な電界を膜内に形成させるため、膜厚方向に電圧を印加しており(図6-5(a))、10倍程度の電荷増倍率を目指している。一方、将来の超高感度化を目指した増倍率向上のためには、膜内の電界をさらに強める必要があるが、固体撮像デバイスに積層された膜に印加できる電圧には制限があることから、従来構造では増倍膜の厚みを薄くする必要がある。しかし、膜厚が薄くなるほど光の吸収が低下し、光の利用効率低下を招く。そこで、膜の厚さに依存することなく内部の電界を強めることができる、新しいデバイス構造の検討に着手した(図6-5(b))。本構造では、電圧を印加する電極(陽極)を、画素電極(陰極)と同一面上に形成することで、膜内の横方向に強い電界を得ることができる。これにより光電変換膜の厚みを保持したまま、光の吸収特性を低下させることなく、高い電荷増倍率を得ることが期待できる。

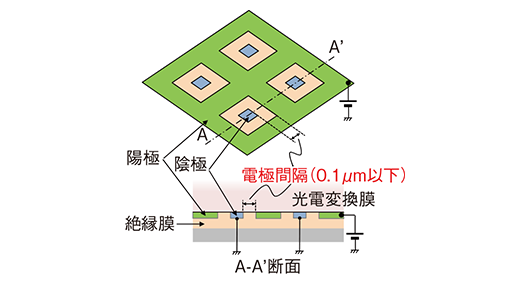

2018年度は、電荷増倍率を100倍程度得るために必要な膜内の電界強度を予備実験の結果を基に推定するとともに、所望の電界強度を得るための電極構造を、電界解析を用いたシミュレーションにより検討した。図6-6に解析により得られた有効な電極構造を示す。ひとつの陰極-陽極対の大きさは非常に小さくなると想定されるため、1画素は複数の陰極-陽極対で構成し、陰極を囲うようにサブミクロン(0.1μm以下)の微細な間隔をあけて陽極を配置したものを多数並べた。この電極構造で電極サイズを最適化することにより、およそ100倍の増倍率を得るための強電界(108V/m)を陰極の近傍に均一に形成できることが分かった。

図6-5 増倍膜積層型撮像デバイスの構造

図6-6 解析に用いた電極構造

| 〔参考文献〕 | |

| (1) | 後藤,本田,渡部,萩原,難波,井口,更屋,小林,日暮,年吉,平本:“画素並列信号処理3層構造イメージセンサの設計,” 第79回応物秋季予稿集,19p-432-7(2018) |

| (2) | 堀,高木,堺,中田,佐藤,大竹,相原:“有機撮像デバイス用信号読み出し回路の微細化技術,” 映情学年次大,13C-1(2018) |